| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

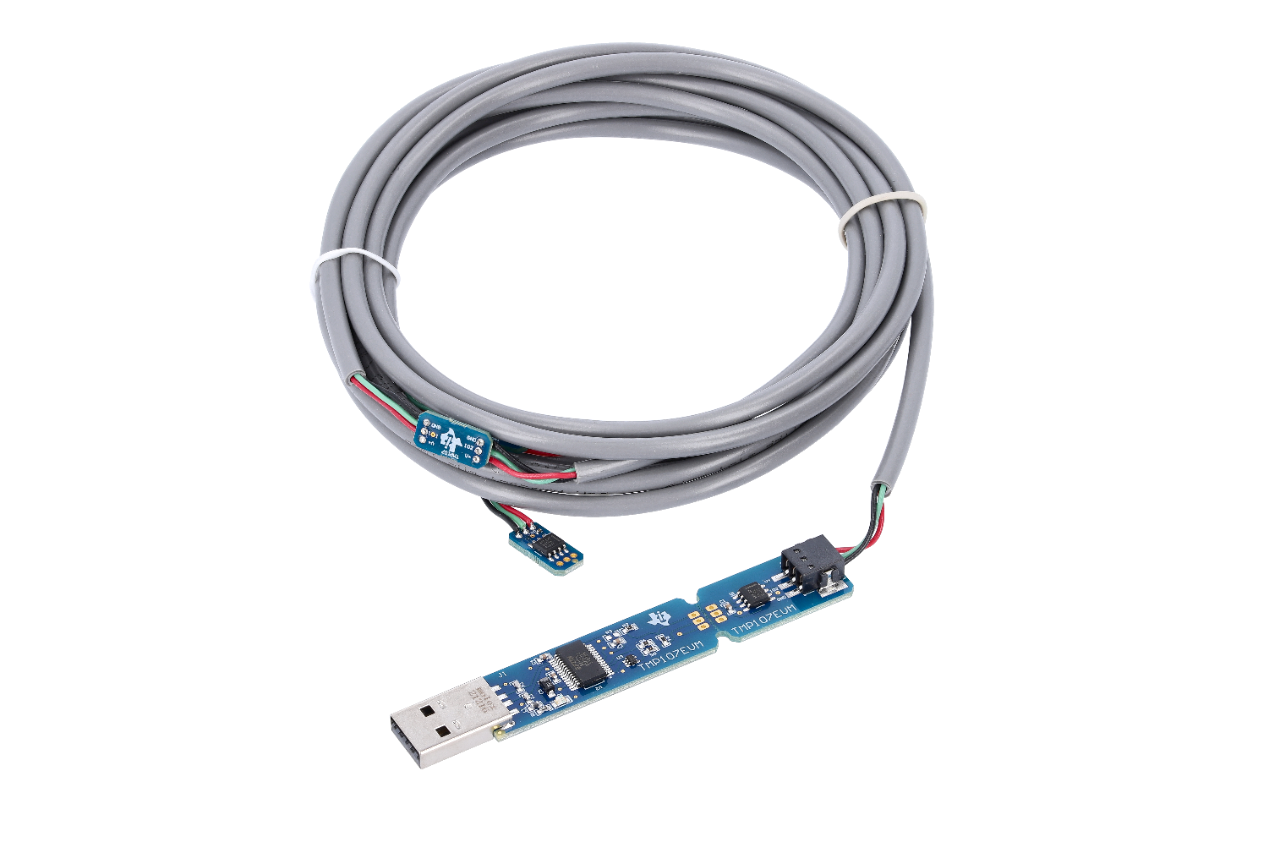

| DigiKey | 296-43192-ND | 2 | 1 | $106.80 | $106.80 | $106.80 | $106.80 | $106.80 | $106.80 |

| Arrow North American Components | TMP107EVM | 0 | 1 | $121.08 | $119.87 | $117.49 | $116.31 | $112.86 | $111.73 |

| AVNET Express | TMP107EVM | 0 | 1 | $108.58 | $108.58 | $108.58 | $108.58 | $108.58 | $108.58 |

| element14 APAC | TMP107EVM | 5 | 1 | * $130.51 | * $130.51 | * $130.51 | * $130.51 | * $130.51 | * $130.51 |

| Farnell | TMP107EVM | 5 | 1 | * $133.00 | * $133.00 | * $133.00 | * $133.00 | * $133.00 | * $133.00 |

| Mouser Electronics | 595-TMP107EVM | 0 | 1 | $115.71 | $115.71 | $115.71 | $115.71 | $115.71 | $115.71 |

| Newark | TMP107EVM | 4 | 1 | $116.05 | $116.05 | $116.05 | $116.05 | $116.05 | $116.05 |

| Texas Instruments | TMP107EVM | 24 | 1 | $89.00 | $89.00 | $89.00 | $89.00 | $89.00 | $89.00 |

| Verical Marketplace | TMP107EVM | 6 | 1 | $102.25 | $114.76 | $114.76 | $114.76 | $114.76 | $114.76 |

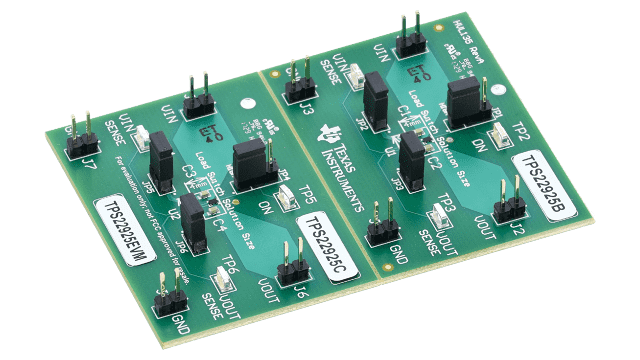

TPS22925EVM 3.6V; 3A; 9mΩ Load Switch Evaluation Module

Texas Instruments

TPS22925EVM 3.6V; 3A; 9mΩ Load Switch Evaluation Module

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-46795-ND | 1 | 1 | $30.00 | $30.00 | $30.00 | $30.00 | $30.00 | $30.00 |

| Arrow North American Components | TPS22925EVM | 0 | 1 | $34.87 | $34.53 | $33.84 | $33.50 | $32.51 | $32.18 |

| AVNET Express | TPS22925EVM | 0 | 1 | $30.50 | $30.50 | $30.50 | $30.50 | $30.50 | $30.50 |

| Mouser Electronics | 595-TPS22925EVM | 1 | 1 | $33.08 | $33.07 | $33.07 | $33.07 | $33.07 | $33.07 |

| Texas Instruments | TPS22925EVM | 21 | 1 | $25.00 | $25.00 | $25.00 | $25.00 | $25.00 | $25.00 |

Sensor AFE Evaluation Board for pH sensors

Texas Instruments

Sensor AFE Evaluation Board for pH sensors

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | LMP91200EVAL/NOPB-ND | 0 | |||||||

| Mouser Electronics | N/A | 0 |

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | LP38502TJ-ADJEV-ND | 0 | 1 | $53.90 | $53.90 | $53.90 | $53.90 | $53.90 | $53.90 |

| Arrow North American Components | LP38502TJ-ADJEV | 0 | 1 | $0.00 | $50.76 | $50.76 | $50.05 | $47.56 | $47.56 |

| AVNET Express | LP38502TJ-ADJEV | 0 | 1 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 |

| Mouser Electronics | 926-LP38502TJ-ADJEV | 0 | 1 | $0.00 | |||||

| Texas Instruments | LP38502TJ-ADJEV | 28 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Win Source | LP38502TJ-ADJEV | 1 | 1 |

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-20568-ND | 0 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | |

| Mouser Electronics | 595-THS6092EVM | 0 | 1 | $0.00 | |||||

| Texas Instruments | THS6092EVM | 20 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

LP8861-Q1 4-Channel LED Driver for Automotive Lighting Evaluation Module

Texas Instruments

LP8861-Q1 4-Channel LED Driver for Automotive Lighting Evaluation Module

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-42589-ND | 2 | 1 | $94.80 | $94.80 | $94.80 | $94.80 | $94.80 | $94.80 |

| Arrow North American Components | LP8861Q1EVM | 0 | 1 | $107.97 | $106.89 | $104.76 | $103.72 | $100.63 | $99.63 |

| AVNET Express | LP8861Q1EVM | 0 | 1 | $96.38 | $96.38 | $96.38 | $96.38 | $96.38 | $96.38 |

| element14 APAC | LP8861Q1EVM | 4 | 1 | * $115.85 | * $115.85 | * $115.85 | * $115.85 | * $115.85 | * $115.85 |

| Farnell | LP8861Q1EVM | 4 | 1 | * $118.05 | * $118.05 | * $118.05 | * $118.05 | * $118.05 | * $118.05 |

| Mouser Electronics | 595-LP8861Q1EVM | 2 | 1 | $102.71 | $102.71 | $102.71 | $102.71 | $102.71 | $102.71 |

| Newark | LP8861Q1EVM | 0 | 1 | $105.48 | $103.01 | $103.01 | $103.01 | $103.01 | $103.01 |

| Texas Instruments | LP8861Q1EVM | 7 | 1 | $79.00 | $79.00 | $79.00 | $79.00 | $79.00 | $79.00 |

| Verical Marketplace | LP8861Q1EVM | 2 | 1 | $114.49 | $95.19 | $95.19 | $95.19 | $95.19 | $95.19 |

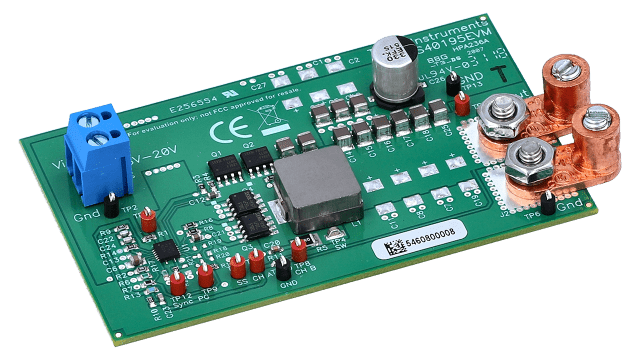

TPS40195 20V Input; 3.3V Output; 20A Evaluation Module

Texas Instruments

TPS40195 20V Input; 3.3V Output; 20A Evaluation Module

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-31161-ND | 2 | 1 | $238.80 | $238.80 | $238.80 | $238.80 | $238.80 | $238.80 |

| Arrow North American Components | TPS40195EVM-001 | 0 | 1 | $265.00 | $262.35 | $0.00 | $254.56 | $246.99 | $0.00 |

| AVNET Europe | TPS40195EVM-001 | 0 | 1 | * $79.55 | * $83.42 | * $78.26 | * $75.68 | * $75.68 | * $75.68 |

| AVNET Express | TPS40195EVM-001 | 0 | 1 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 |

| element14 APAC | TPS40195EVM-001 | 0 | 1 | * $63.01 | * $63.01 | * $63.01 | * $63.01 | * $63.01 | * $63.01 |

| Farnell | TPS40195EVM-001 | 0 | 6 | * $0.00 | * $58.71 | * $58.71 | * $58.71 | * $58.71 | * $58.71 |

| Mouser Electronics | 595-TPS40195EVM-001 | 0 | 1 | $258.72 | $258.72 | $258.72 | $258.72 | $258.72 | $258.72 |

| Newark | TPS40195EVM-001 | 0 | 6 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 |

| Texas Instruments | TPS40195EVM-001 | 13 | 1 | $199.00 | $199.00 | $199.00 | $199.00 | $199.00 | $199.00 |

| Verical Marketplace | TPS40195EVM-001 | 58 | 1 | $56.74 | $56.71 | $53.91 | $53.91 | $53.91 | $53.91 |

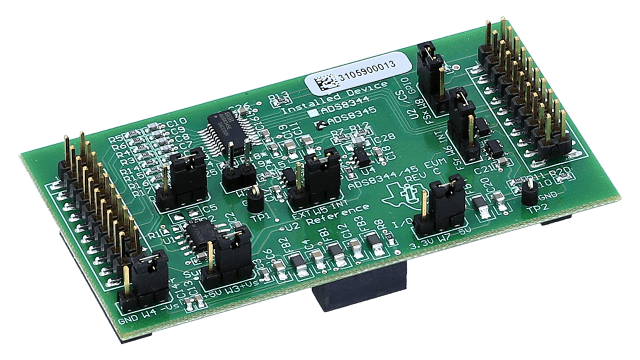

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-19921-ND | 2 | 1 | $239.99 | $239.99 | $239.99 | $239.99 | $239.99 | $239.99 |

| Arrow North American Components | ADS8345EVM | 0 | 1 | $272.08 | $269.36 | $264.00 | $261.36 | $253.60 | $251.06 |

| AVNET Europe | ADS8345EVM | 0 | 1 | * $79.55 | * $83.42 | * $78.26 | * $75.68 | * $75.68 | * $75.68 |

| AVNET Express | ADS8345EVM | 0 | 1 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 |

| Farnell | ADS8345EVM | 0 | 1 | * $48.56 | * $48.56 | * $48.56 | * $48.56 | * $48.56 | * $48.56 |

| Mouser Electronics | 595-ADS8345EVM | 1 | 1 | $195.00 | $195.00 | $195.00 | $195.00 | $195.00 | $195.00 |

| Newark | ADS8345EVM | 0 | 6 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 | $50.73 |

| Texas Instruments | ADS8345EVM | 10 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Verical Marketplace | ADS8345EVM | 14 | 1 | $50.35 | $50.35 | $50.35 | $50.35 | $50.35 | $50.35 |

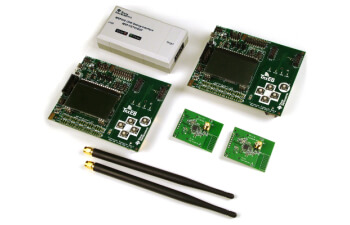

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-36405-ND | 7 | 1 | $373.75 | $373.75 | $373.75 | $373.75 | $373.75 | $373.75 |

| Arrow North American Components | CC1200DK | 0 | 1 | $407.52 | $403.45 | $395.42 | $391.47 | $379.84 | $376.04 |

| AVNET Asia Pacific | CC1200DK | 0 | 1 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 | $0.00 |

| AVNET Europe | CC1200DK | 0 | 1 | * $376.95 | * $372.12 | * $362.80 | * $358.42 | * $358.42 | * $358.42 |

| element14 APAC | CC1200DK | 2 | 1 | * $438.45 | * $438.45 | * $438.45 | * $438.45 | * $438.45 | * $438.45 |

| Farnell | CC1200DK | 2 | 1 | * $446.80 | * $446.80 | * $446.80 | * $446.80 | * $446.80 | * $446.80 |

| Mouser Electronics | 595-CC1200DK | 34 | 1 | $388.73 | $388.73 | $388.73 | $388.73 | $388.73 | $388.73 |

| Newark | CC1200DK | 1 | 1 | $399.22 | $389.86 | $389.86 | $389.86 | $389.86 | $389.86 |

| Texas Instruments | CC1200DK | 62 | 1 | $299.00 | $299.00 | $299.00 | $299.00 | $299.00 | $299.00 |

| Verical Marketplace | CC1200DK | 36 | 1 | $427.14 | $404.05 | $398.67 | $398.67 | $398.67 | $398.67 |

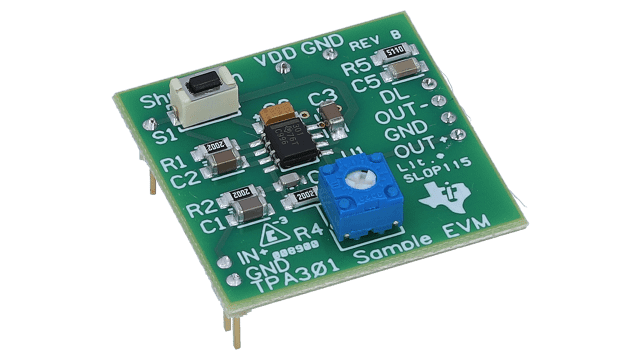

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 296-10834-ND | 2 | 1 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 | $58.80 |

| AVNET Europe | TPA301EVM | 0 | 1 | * $67.90 | * $65.83 | * $62.14 | * $60.42 | * $60.42 | * $60.42 |

| AVNET Express | TPA301EVM | 0 | 1 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 | $59.78 |

| Mouser Electronics | 595-TPA301EVM | 0 | 1 | $65.17 | $65.17 | $65.17 | $65.17 | $65.17 | $65.17 |

| Texas Instruments | TPA301EVM | 15 | 1 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 | $49.00 |

| Verical Marketplace | TPA301EVM | 6 | 1 | $62.27 | $62.27 | $62.27 | $62.27 | $62.27 | $62.27 |