EV1HMC412BMS8G

Analog Devices Inc.

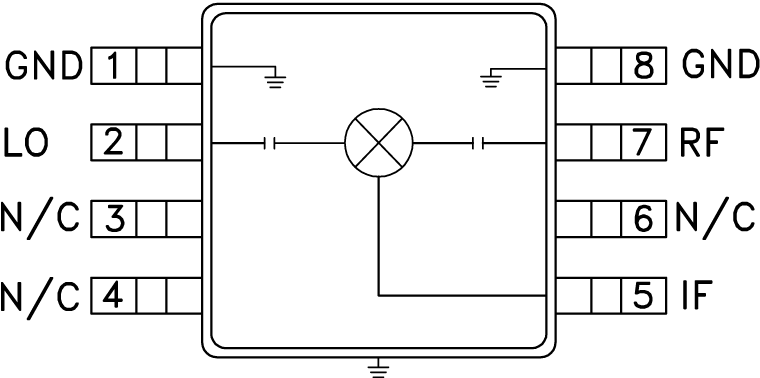

The HMC412BMS8GE is a passive double-balancedmixer that operates from 8 to 16 GHz. TheHMC412BMS8GE operates with LO drive levelsbetween 9 to 15 dBm and provides 8 dB of conversionloss across the entire specified frequency band. Thismixer requires no external components or bias.Applications Long Haul Radio Platforms Microwave Radio VSAT

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 505-EV1HMC412BMS8G-ND | 1 | 1 | $313.70 | $313.70 | $313.70 | $313.70 | $313.70 | $313.70 |

| Analog Devices Inc | EV1HMC412BMS8G | 0 | $299.40 | $299.40 | $299.40 | $299.40 | $299.40 | $299.40 | |

| Arrow North American Components | EV1HMC412BMS8G | 0 | 1 | $277.58 | $277.58 | $277.58 | $277.58 | $277.58 | $277.58 |

| Mouser Electronics | 584-EV1HMC412BMS8G | 2 | $252.94 | ||||||

| Verical Marketplace | EV1HMC412BMS8G | 24 | 1 | $296.25 | $296.25 | $296.25 | $296.25 | $296.25 | $296.25 |

EV1HMC424ALH5

Analog Devices Inc.

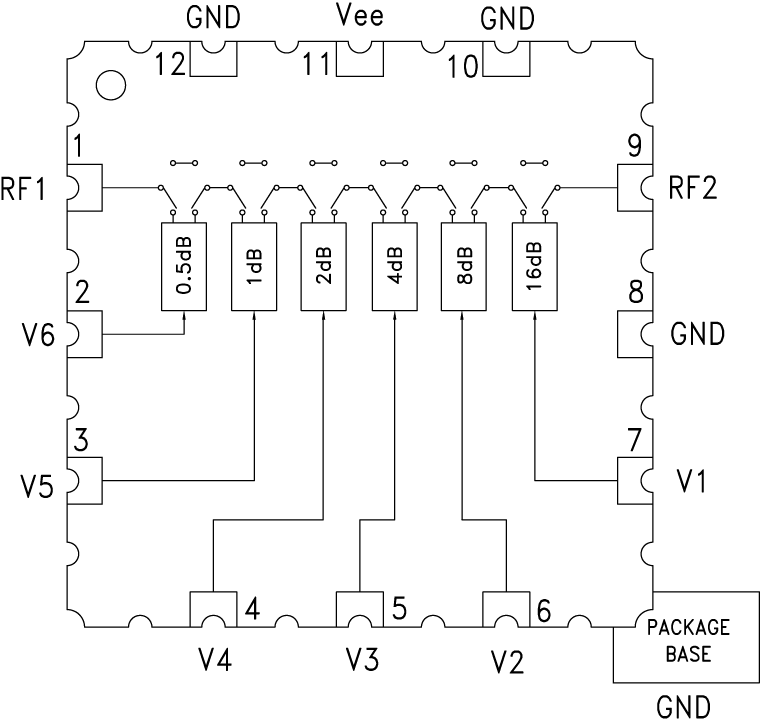

The HMC424ALH5 is a broadband 6-bit GaAs MMIC digital attenuator housed in a hermetic SMT leadless package. Covering DC to 13 GHz, the insertion loss is less than 3.5 dB typical. The attenuator bit values are 0.5 (LSB), 1, 2, 4, 8, and 16 dB for a total attenuation of 31.5 dB. Attenuation accuracy is excellent at ?0.5 dB typical step error with an IIP3 of +34 dBm. Six control voltage inputs, toggled between 0 and -5V, are used to select each attenuation state. A single Vee bias of -5V allows operation at frequencies down to DC. The HMC424ALH5 is compatible with standard and lead free surface mount manufacturing techniques and is suitable for high reliability military, industrial and space applications.Applications Telecom Infrastructure Military Radio, Radar & ECM Space Systems Test Instrumentation

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 1127-3268-ND | 2 | 1 | $414.82 | $414.82 | $414.82 | $414.82 | $414.82 | $414.82 |

| Analog Devices Inc | EV1HMC424ALH5 | 0 | $345.53 | $345.53 | $345.53 | $345.53 | $345.53 | $345.53 | |

| Arrow North American Components | EV1HMC424ALH5 | 0 | 1 | $376.31 | $372.55 | $365.14 | $361.48 | $350.75 | $347.24 |

| element14 APAC | EV1HMC424ALH5 | 3 | 1 | * $441.48 | * $441.48 | * $441.48 | * $441.48 | * $441.48 | * $441.48 |

| Farnell | EV1HMC424ALH5 | 2 | 1 | * $416.17 | * $416.17 | * $416.17 | * $416.17 | * $416.17 | * $416.17 |

| Mouser Electronics | 584-EV1HMC424ALH5 | 3 | 1 | $352.61 | $352.61 | $352.61 | $352.61 | $352.61 | $352.61 |

| Newark | EV1HMC424ALH5 | 3 | 1 | $412.66 | $412.66 | $412.66 | $412.66 | $412.66 | $412.66 |

| Verical Marketplace | EV1HMC424ALH5 | 26 | 1 | $391.75 | $363.65 | $354.08 | $354.08 | $354.08 | $354.08 |

EV1HMC424ALP3

Analog Devices Inc.

The HMC424ALP3E is a broadband, 6-bit, gallium arsenide (GaAs), digital attenuator in low cost, leadless surface-mount package with a 31.5 dB attenuation control range in 0.5 dB steps.The HMC424ALP3E offers excellent attenuation accuracy of ?(0.2 dB + 4% of attenuation state) and high input linearity with a typical insertion loss of less than 4 dB over the specified frequency range from 0.1 GHz to 13.0 GHz. The attenuator bit values are 0.5 dB (LSB), 1 dB, 2 dB, 4 dB, 8 dB, and 16 dB for a total attenuation of 31.5 dB with a ?0.5 dB typical step error.The device allows a user to program the attenuation state via six parallel control inputs toggled between 0 V and VEE.The HMC424ALP3E operates with a single negative supply voltage from ?3 V to ?5 V, and requires an external level shifter to interface with a CMOS/transistor to transistor logic (TTL) interface.The HMC424ALP3E comes in a RoHS compliant, compact, 3 mm ? 3 mm, 16-lead lead frame chip scale package (LFCSP).Applications Cellular infrastructure Microwave radios and very small aperture terminals (VSATs) Test equipment and sensors Intermediate frequency (IF) and RF designs Military and space

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 1127-3080-ND | 5 | 1 | $317.50 | $317.50 | $317.50 | $317.50 | $317.50 | $317.50 |

| Analog Devices Inc | EV1HMC424ALP3 | 0 | $275.49 | $275.49 | $275.49 | $275.49 | $275.49 | $275.49 | |

| Arrow North American Components | EV1HMC424ALP3 | 0 | 1 | $276.94 | $276.94 | $276.94 | $276.94 | $276.94 | $276.94 |

| element14 APAC | EV1HMC424ALP3 | 2 | 1 | * $348.39 | * $348.39 | * $348.39 | * $348.39 | * $348.39 | * $348.39 |

| Farnell | EV1HMC424ALP3 | 2 | 1 | * $270.76 | * $270.76 | * $270.76 | * $270.76 | * $270.76 | * $270.76 |

| Mouser Electronics | 584-EV1HMC424ALP3 | 1 | 1 | $233.83 | $233.83 | $233.83 | $233.83 | $233.83 | $233.83 |

| Newark | EV1HMC424ALP3 | 2 | 1 | $311.81 | $311.81 | $311.81 | $311.81 | $311.81 | $311.81 |

| Verical Marketplace | EV1HMC424ALP3 | 34 | 1 | $299.85 | $299.85 | $299.85 | $299.85 | $299.85 | $299.85 |

EV1HMC468ALP3

Analog Devices Inc.

The HMC468ALP3E is a broadband 3-bit GaAs IC digital attenuators in a low cost leadless surface mount package. Covering DC to 6.0 GHz, the insertion loss is less than 1 dB typical up to 4 GHz. The attenuator bit values are 1 (LSB), 2 and 4 dB for a total attenuation of 7 dB. Attenuation accuracy is excellent at ?0.4 dB typical step error with an IIP3 of +55 dBm. Three control voltage inputs, toggled between 0 and +5V, are used to select each attenuation state. A single Vdd bias of +5V is required.APPLICATIONS Cellular; UMTS/3G Infrastructure? Fixed Wireless & WLL? Microwave Radio & VSAT? Test Equipment

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 1127-2799-ND | 0 |

EV1HMC525ALC4

Analog Devices Inc.

The HMC525ALC4 is a compact gallium arsenide (GaAs), monolithic microwave integrated circuit (MMIC), in phase quadrature (I/Q) mixer in a 24-terminal, RoHS compliant, ceramic leadless chip carrier (LCC) package. The device can be used as either an image reject mixer or a single sideband (SSB) upconverter. The mixer uses two standard double balanced mixer cells and a 90? hybrid fabricated in a GaAs, metalsemiconductor field effect transistor (MESFET) process. The HMC525ALC4 is a much smaller alternative to a hybrid style image reject mixer and a SSB upconverter assembly. The HMC525ALC4 eliminates the need for wire bonding, allowing the use of surface-mount manufacturing techniques. Applications Microwave and very small aperture terminal radios Test equipment Point to point radios Military electronic warfare; electronic countermeasure; and command, control, communications, and intelligence

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 505-EV1HMC525ALC4-ND | 1 | 1 | $384.94 | $384.94 | $384.94 | $384.94 | $384.94 | $384.94 |

| Analog Devices Inc | EV1HMC525ALC4 | 0 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | |

| Arrow North American Components | EV1HMC525ALC4 | 0 | 1 | $348.25 | $348.25 | $348.25 | $348.25 | $348.25 | $348.25 |

| element14 APAC | EV1HMC525ALC4 | 3 | 1 | * $420.08 | * $420.08 | * $420.08 | * $420.08 | * $420.08 | * $420.08 |

| Farnell | EV1HMC525ALC4 | 3 | 1 | * $386.20 | * $386.20 | * $386.20 | * $386.20 | * $386.20 | * $386.20 |

| Newark | EV1HMC525ALC4 | 3 | 1 | $383.40 | $383.40 | $383.40 | $383.40 | $383.40 | $383.40 |

| Verical Marketplace | EV1HMC525ALC4 | 17 | 1 | $374.57 | $374.57 | $374.57 | $374.57 | $374.57 | $374.57 |

| Win Source | EV1HMC525ALC4 | 6040 |

EV1HMC554ALC3B

Analog Devices Inc.

The HMC554ALC3B is a general-purpose, double balanced mixer in a leadless RoHS compliant leadless chip carrier (LCC) package that can be used as an upconverter or downconverter between 10 GHz and 20 GHz. This mixer is fabricated in a gallium arsenide (GaAs) metal semiconductor field effect transistor (MESFET) process and requires no external?components or matching circuitry. The HMC554ALC3B provides excellent local oscillator (LO) to RF and LO to intermediate frequency (IF) isolation due to optimized balun structures. The RoHS compliant HMC554ALC3B eliminates the need for wire bonding and is compatible with high volume surface-mount manufacturing techniques.Applications Microwave and very small aperture terminal (VSAT) radios Test equipment Military electronic warfare (EW); electronic countermeasure (ECM); and command, control, communications and intelligence (C3I)

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 505-EV1HMC554ALC3B-ND | 1 | 1 | $350.84 | $350.84 | $350.84 | $350.84 | $350.84 | $350.84 |

| Analog Devices Inc | EV1HMC554ALC3B | 0 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | |

| Arrow North American Components | EV1HMC554ALC3B | 0 | 1 | $327.10 | $323.83 | $317.39 | $314.21 | $304.88 | $301.83 |

| element14 APAC | EV1HMC554ALC3B | 2 | 1 | * $382.85 | * $382.85 | * $382.85 | * $382.85 | * $382.85 | * $382.85 |

| Farnell | EV1HMC554ALC3B | 2 | 1 | * $351.99 | * $351.99 | * $351.99 | * $351.99 | * $351.99 | * $351.99 |

| Newark | EV1HMC554ALC3B | 2 | 1 | $349.44 | $349.44 | $349.44 | $349.44 | $349.44 | $349.44 |

| Verical Marketplace | EV1HMC554ALC3B | 25 | 1 | $340.52 | $340.52 | $340.52 | $340.52 | $340.52 | $340.52 |

EV1HMC5805ALS6

Analog Devices Inc.

The HMC5805ALS6 is a GaAs pHEMT MMIC Distributed Power Amplifier which operates between DCand 40 GHz. The amplifier provides 11.5 dB of gain,29 dBm output IP3 and +24 dBm of output power at1 dB gain compression while requiring 175 mA froma +10 V supply. The HMC5805ALS6 is ideal for EW,ECM, Radar and test equipment applications. TheHMC5805ALS6 amplifier I/Os are internally matchedto 50 Ohms and the 6x6 mm SMT package is wellsuited for automated assembly techniques.Applications Test instrumentation Microwave radio and VSAT Military and space Telecom infrastructure Fiber optics

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 505-EV1HMC5805ALS6-ND | 2 | 1 | $1,151.72 | $1,151.72 | $1,151.72 | $1,151.72 | $1,151.72 | $1,151.72 |

| Analog Devices Inc | EV1HMC5805ALS6 | 0 | $879.36 | $879.36 | $879.36 | $879.36 | $879.36 | $879.36 | |

| Arrow North American Components | EV1HMC5805ALS6 | 0 | 1 | $863.39 | $863.39 | $863.39 | $863.39 | $863.39 | $863.39 |

| element14 APAC | EV1HMC5805ALS6 | 3 | 1 | * $1,038.82 | * $1,038.82 | * $1,038.82 | * $1,038.82 | * $1,038.82 | * $1,038.82 |

| Farnell | EV1HMC5805ALS6 | 3 | 1 | * $956.27 | * $956.27 | * $956.27 | * $956.27 | * $956.27 | * $956.27 |

| Mouser Electronics | 584-EV1HMC5805ALS6 | 4 | 1 | $952.70 | $952.70 | $952.70 | $952.70 | $952.70 | $952.70 |

| Newark | EV1HMC5805ALS6 | 3 | 1 | $916.56 | $916.56 | $916.56 | $916.56 | $916.56 | $916.56 |

| Verical Marketplace | EV1HMC5805ALS6 | 18 | 1 | $906.37 | $906.37 | $906.37 | $906.37 | $906.37 | $906.37 |

EV1HMC6147ALC5A

Analog Devices Inc.

The HMC6147ALC5A is a compact GaAs MMIC I/Q downconverter in a leadless RoHS compliant SMT package. This device provides a small signal conversion gain of 13 dB with 25 dBc of sideband rejection. The HMC6147ALC5A utilizes a low noise amplifier to drive the I/Q mixer where the LO is driven by a X2 multiplier. IF1 and IF2 mixer inputs are provided and an external 90? hybrid is needed to select the required sideband.The I/Q mixer topology reduces the need for filtering of the unwanted sideband. The HMC 6147ALC5A is a much smaller alternative to hybrid style single sideband converter assemblies and it eliminates the need for wire bonding by allowing the use of surface mount manufacturing techniques.Applications Point-to-Point & Point-to-Multi-Point Radio Military Radar, EW & ELINT Satellite Communications Sensors??

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 1127-3390-ND | 1 | 1 | $360.59 | $360.59 | $360.59 | $360.59 | $360.59 | $360.59 |

| Analog Devices Inc | EV1HMC6147ALC5A | 0 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | |

| Arrow North American Components | EV1HMC6147ALC5A | 0 | 1 | $342.74 | $339.31 | $332.56 | $329.23 | $319.45 | $316.26 |

| Mouser Electronics | 584-EV1HMC6147ALC5A | 1 | 1 | $357.90 | $357.90 | $357.90 | $357.90 | $357.90 | $357.90 |

| Newark | EV1HMC6147ALC5A | 0 | $407.21 | $378.12 | $351.28 | $335.61 | $335.61 | $335.61 | |

| Verical Marketplace | EV1HMC6147ALC5A | 38 | 1 | $356.80 | $372.04 | $367.08 | $367.08 | $367.08 | $367.08 |

EV1HMC647ALP6

Analog Devices Inc.

The HMC647ALP6E is a 6-bit digital phase shifter which is rated from 2.5 to 3.1 GHz, providing 360 degrees of phase coverage, with a LSB of 5.625 degrees. The HMC647ALP6E features very low RMS phase error of 1.5 degrees and extremely low insertion loss variation of ?0.4 dB across all phase states. This high accuracy phase shifter is controlled with positive control logic of 0/+5V The HMC647ALP6E is housed in a compact 6x6 mm plastic leadless SMT package and is internally matched to 50 Ohms with no external components.APPLICATIONS EW Receivers Weather & Military Radar Satellite Communications Beamforming Modules Phase Cancellation

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 1127-3195-ND | 1 | 1 | $510.16 | $510.16 | $510.16 | $510.16 | $510.16 | $510.16 |

| Analog Devices Inc | EV1HMC647ALP6 | 0 | $485.35 | $485.35 | $485.35 | $485.35 | $485.35 | $485.35 | |

| Arrow North American Components | EV1HMC647ALP6 | 0 | 1 | $480.55 | $475.74 | $466.27 | $461.61 | $447.90 | $443.42 |

| element14 APAC | EV1HMC647ALP6 | 4 | 1 | * $556.73 | * $556.73 | * $556.73 | * $556.73 | * $556.73 | * $556.73 |

| Farnell | EV1HMC647ALP6 | 4 | 1 | * $489.11 | * $489.11 | * $489.11 | * $489.11 | * $489.11 | * $489.11 |

| Mouser Electronics | 584-EV1HMC647ALP6 | 6 | 1 | $525.80 | $525.80 | $525.80 | $525.80 | $525.80 | $525.80 |

| Newark | EV1HMC647ALP6 | 2 | 1 | $658.18 | $658.18 | $658.18 | $658.18 | $658.18 | $658.18 |

| Verical Marketplace | EV1HMC647ALP6 | 1 | 1 | $500.26 | $500.26 | $500.26 | $500.26 | $500.26 | $500.26 |

EV1HMC6505ALC5

Analog Devices Inc.

The HMC6505A is a compact gallium arsenide (GaAs),pseudomorphic (pHEMT), monolithic microwave integratedcircuit (MMIC) upconverter in a RoHS compliant package thatoperates from 5.5 GHz to 8.6 GHz. This device provides a smallsignal conversion gain of 15 dB with 22 dBc of sidebandrejection. The HMC6505A uses a variable gain amplifier (VGA)preceded by an in-phase and quadrature (I/Q) mixer that isdriven by an active local oscillator (LO). The IF1 and IF2 mixerinputs are provided, and an external 90? hybrid is needed toselect the required sideband. The I/Q mixer topology reducesthe need for filtering of unwanted sideband. The HMC6505Ais a smaller alternative to hybrid style single sideband (SSB)upconverter assemblies, and it eliminates the need for wirebonding by allowing the use of surface-mount manufacturingtechniques.The HMC6505A is available in 5 mm ? 5 mm, 32-terminalleadless chip carrier (LCC) package and operates over a ?40?Cto +85?C temperature range. An evaluation board for theHMC6505A is also available upon request. Applications Point to point and point to multipoint radios Military radars, electronic warfare (EW), and electronic intelligence (ELINT) Satellite communications Sensors

| Distributor | SKU | Stock | MOQ | 1 | 10 | 50 | 100 | 1,000 | 10,000 |

|---|---|---|---|---|---|---|---|---|---|

| DigiKey | 505-EV1HMC6505ALC5-ND | 1 | 1 | $350.84 | $350.84 | $350.84 | $350.84 | $350.84 | $350.84 |

| Analog Devices Inc | EV1HMC6505ALC5 | 0 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | $330.37 | |

| Arrow North American Components | EV1HMC6505ALC5 | 0 | 1 | $314.69 | $314.69 | $314.69 | $314.69 | $314.69 | $314.69 |

| element14 APAC | EV1HMC6505ALC5 | 4 | 1 | * $382.36 | * $382.36 | * $382.36 | * $382.36 | * $382.36 | * $382.36 |

| Farnell | EV1HMC6505ALC5 | 4 | 1 | * $351.99 | * $351.99 | * $351.99 | * $351.99 | * $351.99 | * $351.99 |

| Mouser Electronics | 584-EV1HMC6505ALC5 | 4 | 1 | $357.90 | $357.90 | $357.90 | $357.90 | $357.90 | $357.90 |

| Newark | EV1HMC6505ALC5 | 4 | 1 | $349.44 | $349.44 | $349.44 | $349.44 | $349.44 | $349.44 |

| Verical Marketplace | EV1HMC6505ALC5 | 19 | 1 | $340.52 | $372.04 | $367.08 | $367.08 | $367.08 | $367.08 |

| Win Source | EV1HMC6505ALC5 | 6120 |