|

|

onsemi

BF245A

|

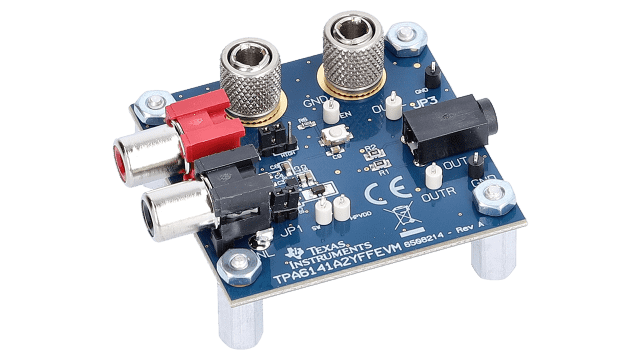

Texas Instruments

TPA6141A2YFFEVM

|

onsemi

KA2902DTF

|

onsemi

PN100A

|

onsemi

PN2907TFR

|

onsemi

MMBFJ305

|

onsemi

MMBT2222

|

Texas Instruments

HPA01202BDKDR

|

Texas Instruments

LM675T/LF05

|

Texas Instruments

ONET8501TYS

|

| Price |

|

|

$50.88 |

|

|

|

|

|

$9.96 |

$3.80 |

$3.29 |

| RoHS |

|

Not Compliant |

Not Compliant |

Compliant |

Not Compliant |

Not Compliant |

Not Compliant |

Compliant |

Compliant |

Yes |

Compliant |

| Lead Status |

|

Yes |

No |

Yes |

No |

|

No |

No |

No |

Yes |

No |

| Power to Bridge Tied Load(Max)(W) |

|

|

|

|

|

|

|

|

300 |

|

|

| Operating Temperature Range(C) |

|

|

|

|

|

|

|

|

0 to 70 |

0 to 70 |

-40 to 100 |

| Power Stage Supply(Min)(V) |

|

|

|

|

|

|

|

|

25 |

|

|

| Power to Parallel Bridge Tied Load(Max)(W) |

|

|

|

|

|

|

|

|

400 |

|

|

| Control Interface |

|

|

|

|

|

|

|

|

Hardware |

|

|

| THD + N @ 1 kHz(%) |

|

|

|

|

|

|

|

|

0.03 |

|

|

| Speaker Channels(Max) |

|

|

|

|

|

|

|

|

4 |

|

|

| SNR(dB) |

|

|

|

|

|

|

|

|

100 |

|

|

| Power Stage Supply(Max)(V) |

|

|

|

|

|

|

|

|

52.5 |

|

|

| Output Power(W) |

|

|

|

|

|

|

|

|

300 |

|

|

| Audio Input Type |

|

|

|

|

|

|

|

|

Analog |

|

|

| Output Current(Typ)(mA) |

|

|

|

|

|

|

|

|

|

4000 |

|

| Architecture |

|

|

|

|

|

|

|

|

|

Bipolar |

|

| Approx. Price (US$) |

|

|

|

|

|

|

|

|

|

2.44 | 1ku |

2.10 | 1ku |

| Total Supply Voltage(Min)(+5V=5, +/-5V=10) |

|

|

|

|

|

|

|

|

|

10 |

|

| Vos (Offset Voltage @ 25C)(Max)(mV) |

|

|

|

|

|

|

|

|

|

10 |

|

| Rating |

|

|

|

|

|

|

|

|

|

Catalog |

|

| Package Size |

|

|

|

|

|

|

|

|

|

mm2 |

|

| Offset Drift(Typ)(uV/C) |

|

|

|

|

|

|

|

|

|

25 |

|

| Rail-to-Rail |

|

|

|

|

|

|

|

|

|

No |

|

| Additional Features |

|

|

|

|

|

|

|

|

|

Decompensated |

|

| CMRR(Typ)(dB) |

|

|

|

|

|

|

|

|

|

90 |

|

| Iq per channel(Typ)(mA) |

|

|

|

|

|

|

|

|

|

18 |

|

| Slew Rate(Typ)(V/us) |

|

|

|

|

|

|

|

|

|

8 |

|

| Number of Channels(#) |

|

|

|

|

|

|

|

|

|

1 |

1 |

| GBW(Typ)(MHz) |

|

|

|

|

|

|

|

|

|

5.5 |

|

| Total Supply Voltage(Max)(+5V=5, +/-5V=10) |

|

|

|

|

|

|

|

|

|

60 |

|

| CMRR(Min)(dB) |

|

|

|

|

|

|

|

|

|

70 |

|

| Iq per channel(Max)(mA) |

|

|

|

|

|

|

|

|

|

50 |

|

| Package Group |

|

|

|

|

|

|

|

|

|

TO-220 |

DIESALE |

| Input Bias Current(Max)(pA) |

|

|

|

|

|

|

|

|

|

2000000 |

|

| BW(Typ)(GHz) |

|

|

|

|

|

|

|

|

|

|

10 |

| Iin,ovl(Min)(mA) |

|

|

|

|

|

|

|

|

|

|

2.5 |

| DJ(Typ)(ps) |

|

|

|

|

|

|

|

|

|

|

6 |

| Data Rate(Gbps) |

|

|

|

|

|

|

|

|

|

|

11.3 |

| In-rms(Typ)(nA) |

|

|

|

|

|

|

|

|

|

|

900 |

| ICC(Max)(mA) |

|

|

|

|

|

|

|

|

|

|

44 |

| DJ ovl(Typ)(ps) |

|

|

|

|

|

|

|

|

|

|

6 |

| Z(Typ)(Ohm) |

|

|

|

|

|

|

|

|

|

|

7000 |

| VCC(V) |

|

|

|

|

|

|

|

|

|

|

3.3 |

| ICC(Nom)(mA) |

|

|

|

|

|

|

|

|

|

|

28 |