|

|

Texas Instruments

DS25BR204EVK/NOPB

|

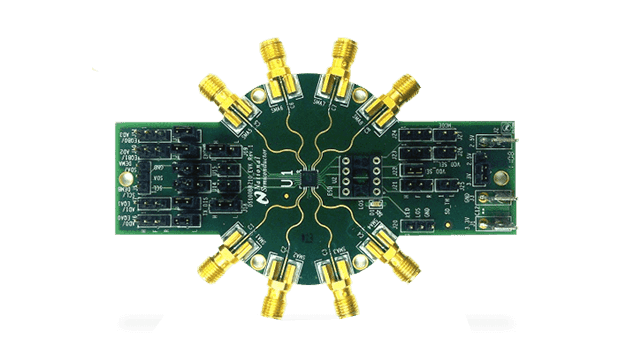

Texas Instruments

DS100BR210EVK/NOPB

|

Texas Instruments

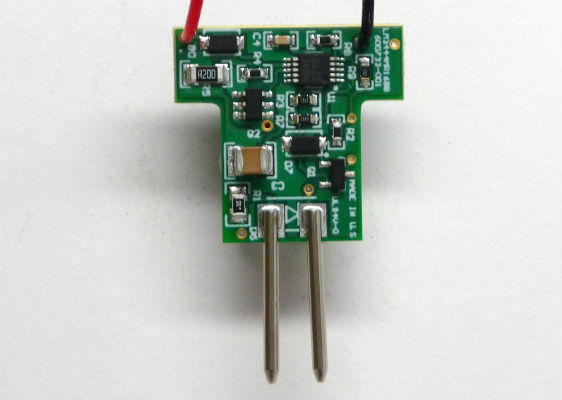

LM3444MR16BBRB/NOPB

|

Texas Instruments

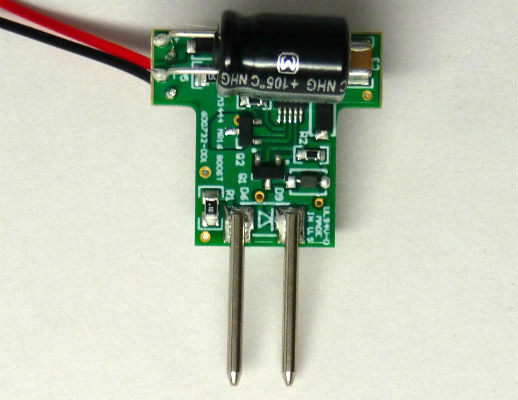

LM3444MR16BSTRB/NOPB

|

Texas Instruments

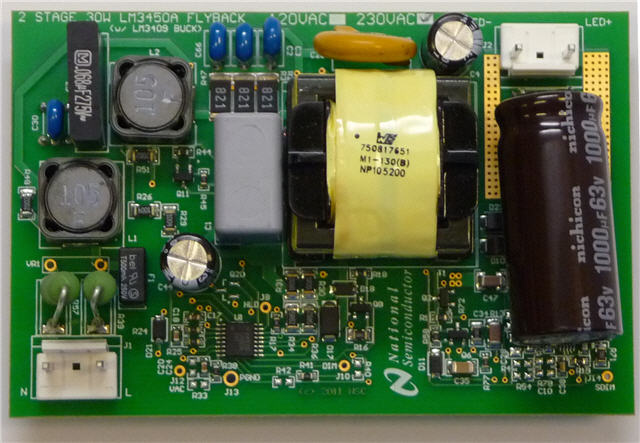

LM3450AEV230V30/NOPB

|

Texas Instruments

LM5064EVK/NOPB

|

Texas Instruments

LMR10515YSDDEMO/NOPB

|

Texas Instruments

LMR64010XMFDEMO/NOPB

|

Texas Instruments

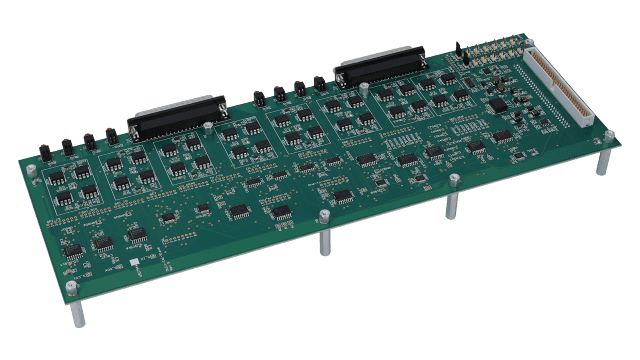

MULTI-CAL-SLAVEKIT

|

Texas Instruments

SERUB-16OVT/NOPB

|

| Price |

|

|

|

|

|

|

|

|

|

|

|

| RoHS |

|

Not Compliant |

Not Compliant |

Not Compliant |

Not Compliant |

Not Compliant |

|

Not Compliant |

Not Compliant |

Not Compliant |

Not Compliant |

| Lead Status |

|

No |

No |

No |

No |

No |

|

No |

No |

No |

No |